在数字电路系统中,门电路是最基础的逻辑单元,它们实现了基本的布尔运算,是构建复杂数字系统的基石。随着半导体技术的发展,CMOS集成电路以其低功耗、高集成度等优势成为现代数字电路的主流实现方式,而集成电路技术本身则是整个信息产业的物理载体。本文将依次介绍门电路的基本概念、CMOS集成电路的工作原理与特点,以及集成电路技术的发展脉络。

一、门电路:数字逻辑的基石

门电路是执行基本逻辑运算的电子电路,其输入和输出信号均为二值逻辑(通常用高、低电平表示“1”和“0”)。最基本的门电路包括与门(AND)、或门(OR)、非门(NOT),由它们可以组合出与非门(NAND)、或非门(NOR)、异或门(XOR)等复合逻辑门。例如,与门仅在所有输入为高电平时输出高电平,实现了逻辑“与”运算。这些门电路的真值表清晰地描述了其输入输出关系,是分析与设计逻辑功能的基础。在早期,门电路由分立元件(如二极管、晶体管)构成,但随着集成电路的出现,它们被高度集成在微小的芯片内。

二、CMOS集成电路:主流实现技术

CMOS(互补金属氧化物半导体)集成电路是目前绝大多数数字电路(如微处理器、存储器)所采用的技术。其核心在于利用PMOS和NMOS两种晶体管互补工作,实现逻辑功能。

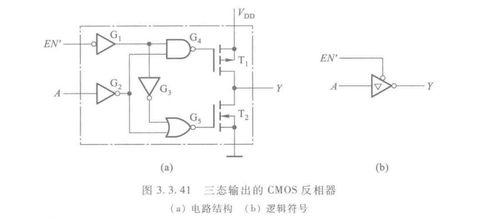

- 基本结构:一个CMOS反相器(非门)由一个PMOS管和一个NMOS管串联构成,两管的栅极相连作为输入,漏极相连作为输出。当输入为低电平时,PMOS导通、NMOS截止,输出被上拉至高电平;输入为高电平时,NMOS导通、PMOS截止,输出被下拉至低电平,从而实现了逻辑取反。

- 主要优点:

- 低静态功耗:在稳定状态下,PMOS和NMOS总有一个截止,从电源到地的直流通路几乎不存在,因此静态功耗极低。

- 高噪声容限:输出电压摆幅接近电源电压,抗干扰能力强。

- 高集成度:制造工艺成熟,晶体管尺寸可微缩,允许在单一芯片上集成数十亿个器件。

- 良好可扩展性:随着工艺进步,性能不断提升。

- 逻辑门实现:通过组合多个MOS管,可以构建各种CMOS逻辑门。例如,CMOS与非门由两个并联的PMOS管和两个串联的NMOS管构成。CMOS技术也支持复杂逻辑功能的直接实现,如复合门(AOI、OAI)。

三、集成电路:技术集成与演进

集成电路(IC)是将晶体管、电阻、电容等元件及互连线制作在一块半导体晶片(通常是硅)上形成的完整电路。按功能可分为数字集成电路、模拟集成电路和混合信号集成电路。数字集成电路(如本文聚焦的门电路、微处理器)处理离散信号,是计算机、通信设备的核心。

- 制造工艺:CMOS IC的制造涉及光刻、刻蚀、掺杂、薄膜沉积等精密工艺,在洁净室中完成。特征尺寸(如7nm、5nm)不断缩小,遵循摩尔定律,推动性能提升和成本下降。

- 设计层次:从底层的晶体管级电路设计,到逻辑门级、功能模块级,直至顶层的系统级设计,辅以硬件描述语言(如Verilog、VHDL)和自动化设计工具(EDA)。

- 发展趋势:随着物理极限的逼近,集成电路技术向三维集成、新器件结构(如FinFET)、新材料(如High-k介质)以及异构集成(将不同工艺的芯片封装在一起)等方向演进,以继续提升性能、能效和功能多样性。

###

从实现基本逻辑运算的门电路,到以CMOS工艺为代表的高效集成电路实现,再到不断演进的集成电路技术本身,三者构成了数字电路设计与应用的完整链条。理解门电路是学习数字逻辑的起点,掌握CMOS原理是深入现代芯片设计的关键,而关注集成电路技术发展则有助于把握信息技术的未来走向。随着人工智能、物联网等新兴领域的兴起,CMOS集成电路及其衍生技术仍将是支撑数字世界的核心引擎。